Product Datasheet Search Results:

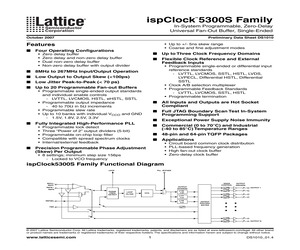

- ISPCLOCK5316S

- Lattice Semiconductor

- In-System Programmable, Zero-Delay, Universal Fan-Out Buffer, Single-Ended

Product Details Search Results:

Latticesemi.com/ISPPAC-CLK5316S-01T64C

{"Category":"Integrated Circuits (ICs)","Differential - Input:Output":"Yes/No","Supplier Device Package":"64-TQFP (10x10)","Operating Temperature":"0\u00b0C ~ 70\u00b0C","Package / Case":"64-LQFP","Input":"HSTL, LVCMOS, LVDS, LVPECL, LVTTL, SSTL","Type":"Clock Generator, Fanout Distribution, Zero Delay Buffer","Ratio - Input:Output":"2:16","Product Photos":"64-LQFP","Datasheets":"ispClock5308S Family Package Diagrams","Frequency - Max":"267MHz","Standard Package":"160","PCN Obsolescence/ EOL":"Tin/Lead Devi...

2179 Bytes - 07:41:47, 21 January 2025

Latticesemi.com/ISPPAC-CLK5316S-01T64I

{"Category":"Integrated Circuits (ICs)","Differential - Input:Output":"Yes/No","Supplier Device Package":"64-TQFP (10x10)","Operating Temperature":"-40\u00b0C ~ 85\u00b0C","Package / Case":"64-LQFP","Input":"HSTL, LVCMOS, LVDS, LVPECL, LVTTL, SSTL","Type":"Clock Generator, Fanout Distribution, Zero Delay Buffer","Ratio - Input:Output":"2:16","Product Photos":"64-LQFP","Datasheets":"ispClock5308S Family Package Diagrams","Frequency - Max":"267MHz","Standard Package":"160","PCN Obsolescence/ EOL":"Tin/Lead De...

2180 Bytes - 07:41:47, 21 January 2025

Latticesemi.com/ISPPAC-CLK5316S-01TN64C

{"Category":"Integrated Circuits (ICs)","Ratio - Input:Output":"2:16","Input":"HSTL, LVCMOS, LVDS, LVPECL, LVTTL, SSTL","Product Photos":"64-LQFP","Family":"Clock/Timing - Clock Generators, PLLs, Frequency Synthesizers","Standard Package":"160","Differential - Input:Output":"Yes/No","Series":"ispClock\u2122","Datasheets":"ispClock5308S Family Package Diagrams","Supplier Device Package":"64-TQFP (10x10)","Divider/Multiplier":"Yes/No","Packaging":"Tray","Frequency - Max":"267MHz","Type":"Clock Generator, Fano...

2117 Bytes - 07:41:47, 21 January 2025

Latticesemi.com/ISPPAC-CLK5316S-01TN64I

{"Category":"Integrated Circuits (ICs)","Ratio - Input:Output":"2:16","Input":"HSTL, LVCMOS, LVDS, LVPECL, LVTTL, SSTL","Product Photos":"64-LQFP","Family":"Clock/Timing - Clock Generators, PLLs, Frequency Synthesizers","Standard Package":"160","Differential - Input:Output":"Yes/No","Series":"ispClock\u2122","Datasheets":"ispClock5308S Family Package Diagrams","Supplier Device Package":"64-TQFP (10x10)","Divider/Multiplier":"Yes/No","Packaging":"Tray","Frequency - Max":"267MHz","Type":"Clock Generator, Fano...

2120 Bytes - 07:41:47, 21 January 2025

Documentation and Support

Use our online request for specific proposed solutions or send your technical question directly to a product specialist at request:

| File Name | File Size (MB) | Document | MOQ | Support |

|---|---|---|---|---|

| PXM1K_DISPCBL_6.pdf | 0.04 | 1 | Request | |

| PXM1K-DISPCBL-15.pdf | 0.04 | 1 | Request | |

| PXM1K_DISPCBL_15.pdf | 0.04 | 1 | Request | |

| PXM1K-DISPCBL-6.pdf | 0.04 | 1 | Request |