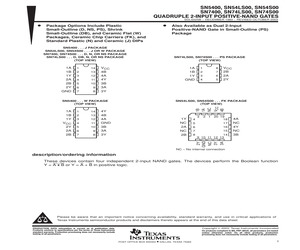

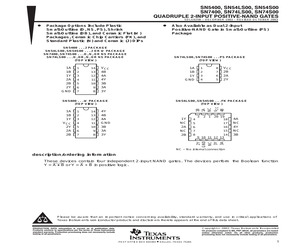

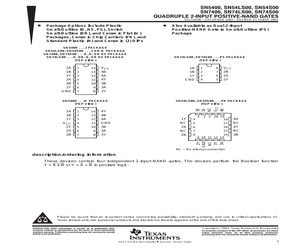

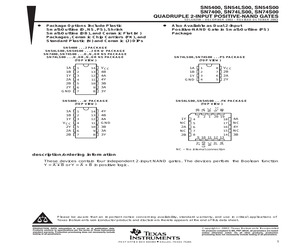

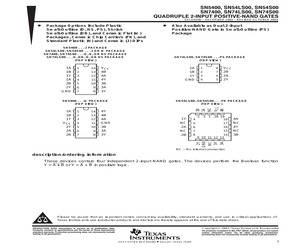

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

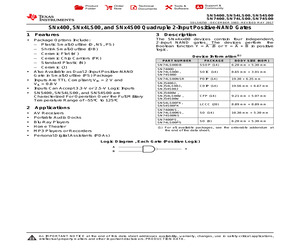

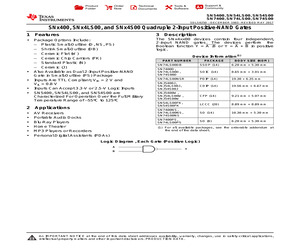

ayers or Recorders Personal Digital Assistants (PDAs) Device Information(1) PART NUMBER PACKAGE BODY SIZE (NOM) SN74LS00DB SSOP (14) 6.20 mm x 5.30 mm SN7400D, SN74LS00D, SN74S00D SOIC (14) 8.65 mm x 3.91 mm SN74LS00NSR PDIP (14) 19.30 x 6.35 mm SNJ5400J, SNJ54LS00J, SNJ54S00J CDIP (14) 19.56 mm x 6.67 mm SNJ5400W, SNJ54LS00W, SNJ54S00W CFP (14) 9.21 mm x 5.97 mm SN54LS00FK, SN54S00FK LCCC (20) 8.89 mm x 8.89 mm SN7400NS, SN74LS00NS, SN74S00NS SO (14) 10.30 mm x 5.30 mm SN7400PS, SN74LS00PS SO (8) 6.20 mm x 5.30 mm (1) For all available packages, see the orderable addendum at the end of the data sheet. Logic Diagram, Each Gate (Positive Logic) A Y B 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA. SN5400, SN54LS00, SN54S00 SN7400, SN74LS00, SN74S00 SDLS025D - DECEMBER 1983 - REVISED MAY 2017 www.ti.com Table of Contents 1 2 3 4 5 6 7 Fe

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

ayers or Recorders Personal Digital Assistants (PDAs) Device Information(1) PART NUMBER PACKAGE BODY SIZE (NOM) SN74LS00DB SSOP (14) 6.20 mm x 5.30 mm SN7400D, SN74LS00D, SN74S00D SOIC (14) 8.65 mm x 3.91 mm SN74LS00NSR PDIP (14) 19.30 x 6.35 mm SNJ5400J, SNJ54LS00J, SNJ54S00J CDIP (14) 19.56 mm x 6.67 mm SNJ5400W, SNJ54LS00W, SNJ54S00W CFP (14) 9.21 mm x 5.97 mm SN54LS00FK, SN54S00FK LCCC (20) 8.89 mm x 8.89 mm SN7400NS, SN74LS00NS, SN74S00NS SO (14) 10.30 mm x 5.30 mm SN7400PS, SN74LS00PS SO (8) 6.20 mm x 5.30 mm (1) For all available packages, see the orderable addendum at the end of the data sheet. Logic Diagram, Each Gate (Positive Logic) A Y B 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA. SN5400, SN54LS00, SN54S00 SN7400, SN74LS00, SN74S00 SDLS025D - DECEMBER 1983 - REVISED MAY 2017 www.ti.com Table of Contents 1 2 3 4 5 6 7 Fe

ayers or Recorders Personal Digital Assistants (PDAs) Device Information(1) PART NUMBER PACKAGE BODY SIZE (NOM) SN74LS00DB SSOP (14) 6.20 mm x 5.30 mm SN7400D, SN74LS00D, SN74S00D SOIC (14) 8.65 mm x 3.91 mm SN74LS00NSR PDIP (14) 19.30 x 6.35 mm SNJ5400J, SNJ54LS00J, SNJ54S00J CDIP (14) 19.56 mm x 6.67 mm SNJ5400W, SNJ54LS00W, SNJ54S00W CFP (14) 9.21 mm x 5.97 mm SN54LS00FK, SN54S00FK LCCC (20) 8.89 mm x 8.89 mm SN7400NS, SN74LS00NS, SN74S00NS SO (14) 10.30 mm x 5.30 mm SN7400PS, SN74LS00PS SO (8) 6.20 mm x 5.30 mm (1) For all available packages, see the orderable addendum at the end of the data sheet. Logic Diagram, Each Gate (Positive Logic) A Y B 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA. SN5400, SN54LS00, SN54S00 SN7400, SN74LS00, SN74S00 SDLS025D - DECEMBER 1983 - REVISED MAY 2017 www.ti.com Table of Contents 1 2 3 4 5 6 7 Fe

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE

e and reel CDIP - J Tube Tube LCCC - FK SN7400N SN7400D SOP - PS CFP - W SN7400N Tube Tape and reel Tube TOP-SIDE MARKING 7400 LS00 S00 SN7400NSR SN7400 SN74LS00NSR 74LS00 SN74S00NSR 74S00 SN74LS00PSR LS00 SN74S00PSR S00 SN74LS00DBR LS00 SNJ5400J SNJ5400J SNJ54LS00J SNJ54LS00J SNJ54S00J SNJ54S00J SNJ5400W SNJ5400W SNJ54LS00W SNJ54LS00W SNJ54S00W SNJ54S00W SNJ54LS00FK SNJ54LS00FK SNJ54S00FK SNJ54S00FK Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. FUNCTION TABLE (each gate) INPUTS A B OUTPUT Y H H L L X H X L H logic diagram, each gate (positive logic) A Y B 2 POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 SDLS025B - DECEMBER 1983 - REVISED OCTOBER 2003 schematic '00 VCC 4 k 130 1.6 k A B Y 1 k GND 'LS00 'S00 VCC 20 k VCC 120 8 k 900 2.8 k 50 A 3.5 k A B 12 k 4 k Y B Y 500 1.5 k 250 3 k GND GND Resistor values shown are nominal. POST OFFICE BOX 655303 * DALLAS, TEXAS 75265 3 SDLS025B - DECEMBE